# **Toolflows for Mapping Convolutional Neural Networks on FPGAs: A Survey and Future Directions**

STYLIANOS I. VENIERIS, ALEXANDROS KOURIS, and CHRISTOS-SAVVAS BOUGANIS, Imperial College London

In the past decade, Convolutional Neural Networks (CNNs) have demonstrated state-of-the-art performance in various Artificial Intelligence tasks. To accelerate the experimentation and development of CNNs, several software frameworks have been released, primarily targeting power-hungry CPUs and GPUs. In this context, reconfigurable hardware in the form of FPGAs constitutes a potential alternative platform that can be integrated in the existing deep-learning ecosystem to provide a tunable balance between performance, power consumption, and programmability. In this article, a survey of the existing CNN-to-FPGA toolflows is presented, comprising a comparative study of their key characteristics, which include the supported applications, architectural choices, design space exploration methods, and achieved performance. Moreover, major challenges and objectives introduced by the latest trends in CNN algorithmic research are identified and presented. Finally, a uniform evaluation methodology is proposed, aiming at the comprehensive, complete, and in-depth evaluation of CNN-to-FPGA toolflows.

$\label{eq:ccs} CCS \ Concepts: \bullet \ General \ and \ reference \ \rightarrow \ Surveys \ and \ overviews; \bullet \ Computing \ methodologies \ \rightarrow \ Neural \ networks; \bullet \ Hardware \ \rightarrow \ Reconfigurable \ logic \ and \ FPGAs; \ Electronic \ design \ automation;$

Additional Key Words and Phrases: Convolutional neural networks, FPGA toolflows, deep learning

### **ACM Reference format:**

Stylianos I. Venieris, Alexandros Kouris, and Christos-Savvas Bouganis. 2018. Toolflows for Mapping Convolutional Neural Networks on FPGAs: A Survey and Future Directions. *ACM Comput. Surv.* 51, 3, Article 56 (June 2018), 39 pages.

https://doi.org/10.1145/3186332

# **1 INTRODUCTION**

Convolutional Neural Networks (CNNs) [47] have demonstrated remarkable performance in Artificial Intelligence (AI) tasks. Being able to achieve high accuracy and frequently outperform traditional AI approaches, CNNs have been employed in a vast range of applications over the past decade, from object detection [53, 72] and classification [78, 82] to drone navigation [20] and autonomous driving [7, 11]. While becoming the state-of-the-art algorithm in AI fields such as machine vision, CNNs are challenged to deal with tasks of continuously increasing complexity. This

Authors' addresses: S. I. Venieris, A. Kouris, and C.-S. Bouganis, Department of Electrical and Electronic Engineering, Imperial College London, SW7 2AZ, London, UK; emails: {stylianos.venieris10, a.kouris16, christos-savvas.bouganis}@ imperial.ac.uk.

This work is licensed under a Creative Commons Attribution International 4.0 License.

2018 Copyright is held by the owner/author(s). ACM 0360-0300/2018/06-ART56 \$15.00 https://doi.org/10.1145/3186332

ACM Computing Surveys, Vol. 51, No. 3, Article 56. Publication date: June 2018.

The support of the EPSRC Centre for Doctoral Training in High Performance Embedded and Distributed Systems (HiPEDS, Grant Reference EP/L016796/1) is gratefully acknowledged.

leads to the design of deeper, more expressive networks at the expense of an increase in computational and memory requirements.

Several software libraries and frameworks have been developed to facilitate the deep learning community with the fast development and high-performance execution of CNNs. Toolflows, such as Caffe,<sup>1</sup> Torch,<sup>2</sup> and Theano,<sup>3</sup> and more recently Caffe2,<sup>4</sup> PyTorch,<sup>5</sup> TensorFlow,<sup>6</sup> MXNet,<sup>7</sup> CoreML,<sup>8</sup> CNTK,<sup>9</sup> and TensorRT,<sup>10</sup> aim to increase the productivity of CNN developers by providing high-level APIs together with high-performance execution of models on power-costly multi-core CPUs, GPUs, and DSPs, or on specialized ASICs [42]. In this context, FPGAs stand as a promising alternative target platform that can bridge the gap between power-hungry programmable architectures and fixed-function power-efficient ASICs. The reconfiguration capabilities of FPGAs could allow the generation of high-performance, low-power hardware mappings of CNNs that can be configured to meet system-level requirements such as throughput, latency, and power in diverse environments, from embedded systems to data centres.

In the past few years, High-Level Synthesis (HLS) tools have demonstrated considerable progress in generating FPGA-based hardware designs from a high level of abstraction [39]. Existing tools such as Xilinx's Vivado HLS, Intel FPGA OpenCL SDK, Maxeler's MaxCompiler, and LegUp [8] employ commonly used programming languages such as C, C++, OpenCL, and Java to facilitate the development of functionally correct hardware designs. Nevertheless, the existing HLS tools aim to yield an efficient design based on the mapping and scheduling of low-level primitive operations, leading to a large design space that does not take into account the inherent structure of the application domain. CNN workloads comprise a well-defined structure consisting of layers, with each layer having a predefined parameterization. The highly structured nature of CNN workloads enables the development of automated domain-specific frameworks that are tailored to CNNs. Such design tools could represent design points along the most important dimensions of CNNs, by capturing crucial application-level parameters, such as the topology of the CNN and the types and configurations of the layers, and map them to architectural parameters.

Currently, various systematic approaches toward the direction of automated mapping of CNNs to FPGAs have been presented. Table 1 lists the published CNN-to-FPGA toolflows in chronological order. Using the proposed frameworks, an optimized FPGA-based accelerator can be generated, given a CNN-FPGA pair. The integration of this class of accelerator generators in the existing deeplearning software frameworks would enable the user community to obtain customized hardware implementations of CNNs, without requiring any hardware design expertise, and thus would enhance the integrability of FPGAs within the deep learning ecosystem.

In this article, a survey of the various CNN-to-FPGA toolflows is presented. For this work, we consider as a toolflow any developed software that performs direct mapping of any input highlevel description of a CNN to a hardware architecture that implements the inference computations of the network, under input-specified resource constraints for a target FPGA platform. The article presents a comparison between these frameworks in terms of supported neural network models,

<sup>&</sup>lt;sup>1</sup>http://caffe.berkeleyvision.org/.

<sup>&</sup>lt;sup>2</sup>http://torch.ch/.

<sup>&</sup>lt;sup>3</sup>http://deeplearning.net/software/theano/.

<sup>&</sup>lt;sup>4</sup>https://caffe2.ai/.

<sup>&</sup>lt;sup>5</sup>http://pytorch.org/.

<sup>&</sup>lt;sup>6</sup>https://www.tensorflow.org/.

<sup>&</sup>lt;sup>7</sup>https://mxnet.apache.org/.

<sup>&</sup>lt;sup>8</sup>https://developer.apple.com/documentation/coreml.

<sup>&</sup>lt;sup>9</sup>https://www.microsoft.com/en-us/cognitive-toolkit/.

<sup>&</sup>lt;sup>10</sup>https://developer.nvidia.com/tensorrt.

| Toolflow Name           | Interface                | Year           |

|-------------------------|--------------------------|----------------|

| fpgaConvNet [85–88]     | Caffe & Torch            | May 2016       |

| DeepBurning [90]        | Caffe                    | June 2016      |

| Angel-Eye [23, 24, 68]  | Caffe                    | July 2016      |

| ALAMO [55-59]           | Caffe                    | August 2016    |

| Haddoc2 [1, 2]          | Caffe                    | September 2016 |

| DNNWEAVER [75, 76]      | Caffe                    | October 2016   |

| Caffeine [98]           | Caffe                    | November 2016  |

| AutoCodeGen [54]        | Proprietary Input Format | December 2016  |

| Finn [19, 84]           | Theano                   | February 2017  |

| FP-DNN [22]             | TensorFlow               | May 2017       |

| Snowflake [10, 21]      | Torch                    | May 2017       |

| SysArrayAccel [91]      | C Program                | June 2017      |

| FFTCodeGen [95-97, 100] | Proprietary Input Format | December 2017  |

Table 1. CNN-to-FPGA Toolflows

interface, generated hardware architecture, methods used to explore the design space, supported arithmetic precision, and performance. Moreover, major challenges introduced by the latest trends in deep learning are identified and possible research directions for automated frameworks are presented. Finally, a benchmark suite together with a uniform evaluation methodology are proposed, aiming at the thorough and in-depth evaluation of CNN-to-FPGA toolflows.

# 2 CNN-TO-FPGA TOOLFLOW CHARACTERISTICS

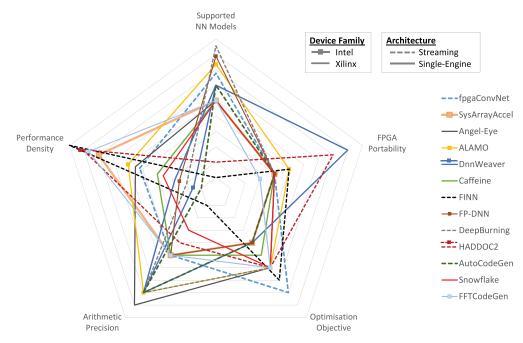

In this section, existing toolflows are analysed with respect to their applicability, design methodology, and performance. The applicability to an end user is investigated based on the supported neural network models, the input interface, and the portability. The design methodology is examined based on the hardware architecture, the design space exploration approach, and the arithmetic precision choices. Finally, the performance is analysed based on the reported results of each toolflow.

# 2.1 Supported Neural Network Models

The application scope of a framework determines the range and type of applications it can target. The majority of the existing toolflows limit their focus on the automated mapping of CNN inference, with FINN focusing on the more specific field of Binarized Neural Networks (BNNs) [37]. The most common types of layers in a CNN are the convolutional (CONV), nonlinear (NONLIN), pooling (POOL), and fully connected (FC) layers [47]. All existing frameworks support these layers, with ALAMO, DeepBurning, DNNWEAVER, and AutoCodeGen also supporting Local Response Normalization (NORM) layers [46]. Moreover, fpgaConvNet, ALAMO, and Snowflake focus mostly on the feature extractor part of CNNs, including CONV, NONLIN, and POOL layers, and offer unoptimized support for FC layers by casting them as CONV layers with 1 × 1 kernels. With respect to compound, irregular CNN building blocks, residual blocks [33] are supported by fpgaConvNet, ALAMO, and Snowflake, Inception modules [82, 83] by fpgaConvNet and Snowflake, and dense blocks [36] by fpgaConvNet. HADDOC2 requires all the weights to be stored on-chip, and therefore the supported model size is constrained by the storage resources of the target device. Currently, DeepBurning and FP-DNN demonstrate the widest range of supported applications by also supporting Recurrent Neural Networks (RNNs) and Long Short-Term Memory (LSTM) networks [34].

## 2.2 Interface

2.2.1 Input. The input interface of an FPGA framework plays a decisive role in its ease-ofuse and accessibility to CNN developers. Caffe constitutes the most widely supported front end with support from seven of the FPGA frameworks, including fpgaConvNet, DeepBurning, Angel-Eye, ALAMO, HADDOC2, DNNWEAVER, and Caffeine, due to its structured, protobuf-based<sup>11</sup> syntax, the vast availability of pretrained models,<sup>12</sup> and the large user community. fpgaConvNet and Snowflake also provide back ends to Torch, and FP-DNN has selected TensorFlow as its front end. With Theano being the first framework to support BNNs, FINN supports Theano-defined BNNs as its input.

SysArrayAccel, AutoCodeGen, and FFTCodeGen have so far adopted custom front ends. SysArrayAccel uses C programs with embedded pragma directives as its front end and exploits the opensource ROSE<sup>13</sup> compiler to capture them. Similarly, AutoCodeGen uses its own proprietary network descriptor, resembling the Caffe syntax. FFTCodeGen employs a custom interface that is based on the YAML<sup>14</sup> serialization framework to specify the CNN model, packaged in a Python 3 wrapper. The design choice of using custom front ends makes it more difficult to integrate with the existing deep-learning toolchains and requires additional infrastructure to make it easily accessible to deep-learning practitioners.

2.2.2 Portability. A primary characteristic of a CNN-to-FPGA toolflow is the range of supported FPGAs. This feature entails the property of design portability. Portability is defined as the degree to which a toolflow can target FPGA platforms with different specifications. A toolflow with high portability would be able to target (1) devices by multiple vendors and families, (2) different setups such as System-on-Chips (SoCs), host-FPGA servers, and standalone FPGA devices, as well as (3) FPGAs of different sizes. Moreover, the choice of development tools and level of design, e.g., RTL, vendor-specific HLS, or open-source HLS, can affect a toolflow's portability.

Currently, the highest degree of portability has been demonstrated by DNNWEAVER. DNNWEAVER generates portable RTL in Verilog and has been reported to target both SoCs and server-grade FPGAs from both Xilinx and Intel, including the Xilinx Zynq XC7Z020 SoC and the larger Intel Stratix V GSD5 and Arria 10 GX115. In a similar manner, HADDOC2 generates RTL, which targets both Intel and Xilinx devices, while AutoCodeGen restricts its scope to RTL targeting Xilinx devices. fpgaConvNet generates its accelerators in Vivado HLS by Xilinx, while Deep-Burning and Angel-Eye use RTL-level design optimized for Xilinx devices. All three toolflows currently support Xilinx SoCs with results reported on Zynq XC7Z020 and XC7Z045. In a similar manner, Snowflake targets Xilinx SoCs, such as Zynq XC7Z045. Caffeine is also developed in Vivado HLS and supports server-grade FPGAs with reported results on Kintex UltraScale KU060 and projected results on the larger Virtex 7 VX690T. At the moment, Caffeine's fully automated components target Xilinx devices that support a runnable SDAccel<sup>15</sup> environment and a PCIe interface between the FPGA and a host. FFTCodeGen generates RTL designs in Verilog and targets the Intel Heterogeneous Research Platform (HARP), consisting of tightly coupled CPU and FPGA with shared memory between them. The target FPGA device is Stratix V GXA7, with a 10-core Intel Xeon E5-2600 v2 CPU as a host.

FP-DNN employs both RTL-level design for its computation engine and Intel OpenCL for interfacing and control logic. In the same direction as Caffeine, FP-DNN targets Intel server-grade

<sup>&</sup>lt;sup>11</sup>https://developers.google.com/protocol-buffers/.

<sup>&</sup>lt;sup>12</sup>http://caffe.berkeleyvision.org/model\_zoo.html.

<sup>&</sup>lt;sup>13</sup>http://rosecompiler.org/.

<sup>&</sup>lt;sup>14</sup>http://yaml.org/.

<sup>&</sup>lt;sup>15</sup>https://www.xilinx.com/products/design-tools/software-zone/sdaccel.html.

FPGAs, with results reported on a Catapult system [9] hosting a Stratix V GSD5 FPGA. Similarly to FP-DNN, SysArrayAccel's hardware is developed in Intel OpenCL with results reported on Arria 10 GT115. FINN generates synthesizable Vivado HLS accelerators and has demonstrated support for the Zynq XC7Z020 and XC7Z045 SoCs as well as the server-grade UltraScale KU115 device in a host-FPGA server setup. Finally, ALAMO's generated RTL designs have demonstrated support for Intel standalone and SoC platforms by targeting the standalone, high-bandwidth Stratix V GXA7 and the Arria 10 GX115 SoC.

## 2.3 Hardware Architecture

The architectures generated by the tools can be taxonomized in two main categories:

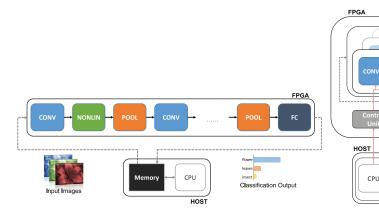

*Streaming architectures.* A streaming architecture typically consists of one distinct hardware block for each layer of the target CNN, where each block is optimized separately to exploit the parallelism of its layer. All the heterogeneous blocks are chained to form a pipeline as depicted in Figure 1. The data proceed through the different parts of the neural network as they are streamed through the architecture. As a result, this design approach exploits the parallelism between layers by means of pipelining and enables their concurrent execution. Nevertheless, the increased efficiency comes with long compilation times, since a new bitstream has to be generated for each CNN.

1) fpgaConvNet. fpgaConvNet employs a streaming architecture that assigns one processing stage per layer. Given a CNN, each layer is mapped to a series of building blocks that are chained together as a coarse pipeline. fpgaConvNet's building blocks include the most commonly utilized components of CNNs, such as convolution and pooling units as well as sliding window structures that provide line-buffering functionality. Moreover, fpgaConvNet employs specialized hardware blocks to map networks with irregular dataflow [33, 36, 82, 83], including Inception, residual, and dense hardware blocks. The performance-resource trade-off of each instantiated block is tuned separately to meet the needs of each layer in the design space exploration phase. fpgaConvNet supports multi-bitstream designs, where different hardware architectures are responsible for executing different parts of the CNN. Currently, this feature requires the full reconfiguration of the FPGA when data have to enter a new architecture, with the potential for multi-FPGA mappings.

fpgaConvNet employs a set of strategies to tailor the generated design to the input CNN while respecting the FPGA resources. For latency-sensitive applications, where the time cost of bitstream-level reconfiguration is prohibitive and batch processing cannot be used to amortise it, fpgaConvNet generates a flexible, latency-optimized architecture, which is time-shared to execute different parts of the network by means of soft, run-time reconfiguration of its datapath. Although this latency-driven design approaches the time-shared, single computation engine paradigm, the hardware stages that comprise the architecture are derived and customized based on the structure of the target network and still operate in a streaming manner. Internally, fpgaConvNet utilises a Synchronous Dataflow (SDF) model [48] to represent architectures. With SDF, the processing rates of all blocks in the system are known a priori and therefore a static schedule is generated to drive the datapath.

*2) DeepBurning*. In a similar approach to fpgaConvNet, DeepBurning's core consists of a library of building blocks that follow the functionality of common neural network components. Currently, the library combines conventional hardware elements, such as nonlinear and pooling operators, with more exotic components, such as dropout units [80]. Given a network structure, the framework's hardware generator builds the neural network architecture by selecting and instantiating blocks from the library, with the appropriate interconnections between them. To meet the target FPGA resource constraints, each block is parameterized so that it can be time-shared both across layers and across parts of a single layer.

Processing Elements

DMA

Mem

Fig. 1. Example of a streaming accelerator architecture.

Fig. 2. Example of a single computation engine accelerator.

Intermediate laver I/O

The architecture adopts a run-time, data-driven mechanism where each block executes whenever data are present at its inputs and largely depends on the time-sharing pattern of each block. After the datapath structure and the memory transactions schedule have been determined, the hardware generator creates a centralized control unit, which is responsible for the data movement between the off- and the on-chip memory. Moreover, a dynamic, run-time control approach is adopted by means of dedicated finite state machines that dynamically control the operation of each time-shared block. DeepBurning's dynamic dataflow approach differs from fpgaConvNet's synchronous dataflow scheme in that DeepBurning does not model the data rates of all blocks and thus requires dynamic control logic, rather than generating a static schedule at compile time.

*3) HADDOC2.* HADDOC2 generates its architecture by modeling the target CNN as a dataflow graph of actors and directly mapping each actor to a dedicated compute unit. This approach results in the mapping of each layer to a hardware stage, similarly to fpgaConvNet and DeepBurning, with layers executing in parallel in a pipelined manner. The hardware mapping of each layer exploits the full unrolling of its input and output feature maps, and the dot products of convolutions. Unrolling along the three aforementioned dimensions increases the required number of multipliers and on-chip storage, rapidly making the available DSPs and memory of the target FPGA device the limiting factors with respect to the size of CNN that can be mapped. To alleviate the excessive requirement for DSPs, HADDOC2 implements all its multipliers solely with logic. Furthermore, since all trained weights are required to be stored on-chip, with off-chip transactions being limited to only the input and output of the network, the weights constitute constant operands for the multipliers. As a result, during synthesis, multiplications with weight values of 0, 1, or powers of 2 are either removed or mapped to direct connections or shift operators, respectively.

With respect to scheduling, HADDOC2's architecture follows a data-driven approach with the schedule generated statically at compile time. This scheduling method is similar to fpgaConvNet's approach and differs from the dynamic control mechanism of DeepBurning. Nevertheless, in contrast to fpgaConvNet and DeepBurning, which support the time-sharing of their resources by means of folding, HADDOC2 does not support partial unrolling and, therefore, given a target device, the maximum model size can be quickly bounded either by the available logic or on-chip storage.

4) AutoCodeGen. AutoCodeGen includes parameterized hardware blocks at the layer level, supporting CONV, POOL, NORM, and FC layers. CONV blocks consist of convolvers that perform dot-product operations in a fully unrolled manner. The instantiated convolvers are

further organized in a tunable number of groups, with input feature maps being shared across all groups. Each convolver group processes the input feature maps with a different set of weights to compute independent output feature maps. Within a group, the inputs are parallelized across the convolvers, followed by an adder tree for the reduction of the partial results. FC layers are mapped to compute units, named FCcores, that tunably exploit the input neurons parallelism and can be time-multiplexed. Similarly, POOL blocks exploit the parallelism of output feature maps to a tunable degree. NORM layers are mapped to a fixed hardware block, which employs a piecewise linear approximation scheme for exponential operations and single-precision floating-point arithmetic to minimise precision loss. In contrast to the data-driven control mechanisms of the rest of the toolflows that generate streaming architectures, AutoCodeGen performs the scheduling and control of each hardware block in a distributed manner, with dedicated, local FSMs coordinating the operation of each block.

5) FINN. FINN adopts the data-driven paradigm and generates a custom streaming architecture based on a BNN's structure. Given a target BNN, each layer is mapped to a dedicated computation engine and all engines are connected in a pipelined manner. With this design, each computation engine can be configured to meet the requirements of the associated layer and match the processing rate of neighbouring engines. In this manner, the overall architecture is tailored to the particular network. With emphasis placed on BNNs, the computation engines differ from conventional CNN hardware designs and are optimized for the efficient mapping of binarized layers, including dedicated hardware for binarized convolutions, max pooling, and batch normalization [40]. FINN expresses binarized convolutions as matrix-vector operations followed by thresholding. To this end, the integral block of the architecture is the Matrix-Vector-Threshold Unit (MVTU), which is optimized to perform the majority of the core binarized operations. In terms of scheduling, FINN's approach lies closer to fpgaConvNet's synchronous dataflow scheme and farther from DeepBurning's dynamic dataflow, with static schedules generated at compile time. Finally, in contrast to fpgaConvNet and DeepBurning and similarly to HADDOC2, all the binarized weights are required to be stored on-chip, with the external memory transfers focusing only on the input and output of the network, imposing a hard limit to the size of networks that can be addressed.

Single computation engines. This design approach favors flexibility over customization. Such an architecture comprises a single computation engine, typically in the form of a systolic array of processing elements or a matrix multiplication unit, that executes the CNN layers sequentially. The control of the hardware and the scheduling of operations is performed by software (Figure 2). This design paradigm consists of a fixed architectural template that can be scaled based on the input CNN and the available FPGA resources. With this scheme, each CNN corresponds to a different sequence of microinstructions that are executable by the hardware. By taking this approach to the extreme, the architecture can be configured and scaled based only on the resources of the target FPGA without targeting a specific CNN and, as a result, after a single compilation, the same bitstream can target many CNNs without the overhead of bitstream-level reconfiguration. Despite the flexibility gains, inefficiencies are introduced due to control mechanisms that resemble those of a processor [27]. Moreover, the one-size-fits-all approach can lead to high variability in the achieved performance across CNNs with different workload characteristics.

1) Angel-Eye. The design principle behind the Angel-Eye framework is based on having a single flexible computation engine that can be programmed and controlled by software. The main computational component is an array of Processing Elements (PEs) with each PE containing a bank of convolvers, an adder tree and an optional pooling path. The input feature maps of a CONV layer are shared across all PEs and each PE processes its inputs with a different set of kernels to produce independent output feature maps. Within a PE, the inputs are parallelized across the convolvers,

followed by the adder tree that combines partial results to produce the output. Overall, the organization of Angel-Eye's and AutoCodeGen's hardware for CONV layers are following the same strategy by organizing convolvers into groups and tunably unrolling with respect to input and output feature maps.

The framework's compiler translates the input CNN to a sequence of instructions from Angel-Eye's custom instruction set and the computation engine executes the instructions. This process corresponds to the sequential execution of the layers in a time-sharing manner. With different CNNs mapped to different instruction sequences, the architecture can be reused to execute various models without recompilation or reconfiguration. In this respect, the hardware design is configured and scaled based only on the available resources of the target device and hence is CNNindependent.

2) ALAMO. In contrast to Angel-Eye, ALAMO customises the generated computation engine to the input CNN. The architecture comprises hardware blocks for POOL, ReLU, and NORM layers, together with a 2D array of compute units that is shared between CONV and FC layers. In CONV layers, the array exploits the parallelism within one input feature map and across multiple output feature maps. At each time instant, each row of the array is responsible for one output feature map, with its columns processing different windows of the same input feature map and combining their partial results synergistically. FC layers are mapped on the same hardware block, by casting them as  $1 \times 1$  CONV layers. Moreover, ALAMO includes a batch normalization block and an elementwise adder. These components are employed as complementary to the main blocks, with the elementwise adder used to implement models with irregular dataflow, including residual networks [33].

Overall, ALAMO's compiler considers the layers that are present in the target CNN and instantiates only the necessary hardware blocks. After the architecture has been generated, the layers are scheduled in a sequential manner. This approach alleviates the problem of allocating resources among different layers of the same type and simplifies the design space to include only the scaling of each hardware block and the scheduling of the layers. The control of the generated accelerator is statically determined at compile time and is encoded as configurations that are loaded sequentially on the accelerator as different parts of the network are executed.

*3)* DNNWEAVER. DNNWEAVER's hardware is based on a parameterized architectural template. The template comprises an array of coarse Processing Units (PUs). Each PU contains a datapath that includes an array of Processing Elements (PEs) that execute CONV and FC layers, followed by dedicated units for NORM, POOL, and NONLIN layers. Within a PU, the CONV and POOL layers are pipelined and their execution is overlapped to exploit the parallelism across layers. The computation of output feature maps for CONV and POOL layers and output neurons for FC layers are scheduled across PUs, with PEs exploiting the parallelism between different elements of each output feature map. Generating a specific instance of the template requires trading between the number of PUs and PEs per PU, which resemble the tunable parameters of Angel-Eye's and AutoCodeGen's architectures. However, in contrast to Angel-Eye, which considers only the available resources of the target device, in DNNWEAVER this tuning is performed at the design space exploration stage and is tailored to the input CNN and constrained by the resources of the target FPGA, as in the case of ALAMO.

4) *Caffeine.* Caffeine's hardware consists of a systolic array of PEs that perform multiplication operations. The array offers scalability in implementing convolution operations by exploiting different levels of parallelism, with optional connections between the output of each PE and dedicated blocks for ReLU and POOL layers. Moreover, support for FC layers is achieved by transforming the matrix-vector multiplications of FC layers into batched convolutions and mapping them to the

existing convolution structure, which allows the reuse of the exact same hardware for both layers. Given a CNN-FPGA pair, the number of parallel PEs is set after the design space exploration phase, so that the hardware will be tailored to the target CNN.

*5) FP-DNN.* Drawing from the fact that CONV and FC layers as well as recurrent connections in RNNs and the gate blocks in LSTMs can be converted to matrix multiplications, FP-DNN generates an architecture with a single generic Matrix Multiplication (*MM*) engine as its core. To balance the computational resources with the external memory bandwidth, tiling is applied on the input matrices, with the tiles processed in a pipelined manner. The *MM* engine processes the tiles in a vector by vector basis by means of a dot-product unit. The dot-product unit consists of an array of multipliers, which fully unrolls all the multiplications of the dot product, followed by an adder tree. To sustain a high utilization of the computational resources and hide the latency of the off-chip memory, FP-DNN employs double buffering for the transfer of matrix tiles. The *MM* engine is time-shared between layers, with nonlinearities and pooling operations applied by separate hardware prior to writing back intermediate results to the off-chip memory. The on-chip memory is organized as a pool of buffers that can be reused by different data at run time to sustain a high utilization. Finally, the layer-specific control logic and the interface with the external memory and the host CPU are implemented with OpenCL-based modules.

*6)* Snowflake. Snowflake's hardware design employs a hierarchical structure that is designed to be controlled by software. At the top level, the architecture comprises a number of hardware compute clusters, organized as an array of tunable size. Each compute cluster contains four parallel compute units (CUs) with a shared buffer for storing feature maps of the current layer and with each CU consisting of four vector MACC (vMAC) units. Internally, each vMAC includes 16 MACC operators, that process 16-bit operands, together with a private buffer for storing weights of the current layer. In a vMAC, the MACC operators can be configured in two modes, based on the type of parallelism to be exploited. The two modes include either assigning the computation of one output feature maps, or assigning the computation of one input feature map to each MACC operators collaborate to produce each output feature map by computing partial results. Moreover, each CU also contains a vector max pooling operator (vMAX). Similarly to FP-DNN, double buffering is employed to overlap computation and communication and hide the latency of the external memory transfers.

From an operational perspective, Snowflake is similar to Angel-Eye's programming flow. The target CNN is translated by a custom compiler, named Snowball, into a series of instructions from Snowflake's instruction set and the generated architecture executes the instructions. This process yields the execution of layers in a sequential manner. Moreover, instead of generating a different hardware design for each target CNN, different models are mapped to their own stream of instructions and the architecture can be reused without bitstream-level reconfiguration. In a similar manner to Angel-Eye, the generated hardware is CNN-independent and is scaled based only on the available resources of the target device.

7) SysArrayAccel. SysArrayAccel follows Caffeine's approach and adopts a 2D systolic array of PEs to execute all the CONV layers of the target CNN. The main differentiating factor from Caffeine's hardware is that SysArrayAccel's architecture has been designed so that each PE is only connected locally to its neighbouring PEs. With this approach, SysArrayAccel avoids the need for large multiplexers at the output of each PE, simplifying the routing and achieving high clock frequencies. Each of the two dimensions of the array corresponds to one loop in the CONV layer and each PE performs a configurable number of parallel MACC operations between inputs

and weights. The shape of the systolic array can be configured at compile time, so that different degrees of parallelism can be exploited based on the workload characteristics of the target CNN and the available FPGA resources. For the rest of the layers, dedicated hardware blocks are instantiated, with FC layers mapped to a 1D array. Given a CNN-FPGA pair, the selection of loops to be mapped on the systolic array and the shape of the array are selected in the design space exploration phase, to optimize the structure of the systolic array for the target CNN.

*8) FFTCodeGen.* FFTCodeGen differentiates from the rest of the existing toolflows in two main ways. First, FFTCodeGen is optimized to target the heterogeneous Intel HARP platform. In this manner, the framework partitions the CNN workload between the CPU and the FPGA, so that the CONV layers time-share the FPGA device and the rest of the layers are executed in software by the CPU. Second, in contrast to the rest of the existing frameworks, FFTCodeGen performs convolutions in the frequency domain by means of an FFT-based algorithm. With this approach, the convolution operations in the space domain are mapped to Hadamard element-by-element products in the frequency domain with decreased computational complexity.

The generated architecture consists of three main components. These comprise 2D FFT and Inverse FFT (IFFT) blocks for transforming feature maps between the space and frequency domains, and a Hadamard-Accumulation (HAC) unit. To perform FFT, FFTCodeGen organizes the input feature maps and the kernels as matrices. To support the flexible and tiled FFT-based processing of CONV layers without the need for hardware reconfiguration, FFTCodeGen combines the conventional Overlap-and-Add (OaD) method with the custom Concatenate-and-Pad (CaP) technique. OaD enables the partitioning of the input matrices into tiles of tunable size. The CaP method adds further flexibility by treating the batch size of the network as another dimension of the input feature maps matrix and introduces a tunable folding factor for the batch. The combination of OaD and CaP enable the derivation of a fixed computation engine that can be time-shared among CONV layers with different input feature map sizes, while sustaining high utilization. In this respect, all tiles of a CONV layer are sequentially fed into the generated accelerator, with double buffering used to hide memory latency, and their partial results are accumulated to produce the output feature maps matrix. Overall, FFTCodeGen uses batch processing to amortize the costs of FFT and IFFT and to enable the CaP method to sustain a high utilization of the generated accelerator by replacing ineffectual zero-padded operations with useful computations.

The 2D FFT and IFFT blocks perform *N*-point FFT and IFFT, respectively, by applying *N*-point 1D FFT on the rows of the input feature maps matrix, followed by an *N*-point 1D FFT on the columns of the transpose of the resulted matrix. The two blocks contain *N* 1D pipelines each, and share common, tunable folding factors for their rows and columns pipelines. The HAC unit performs elementwise multiplication-accumulation and comprises an array of MACC operators, which is parameterized with respect to its size. FFTCodeGen also comprises software modules for the execution of NONLIN, POOL, and FC layers by the CPU. Overall, the processing of CONV layers by the FPGA and the rest of the operations by the CPU are executed in a pipelined manner.

### 2.4 Design Space Exploration

Based on the parameterization and organization of its hardware, a toolflow defines a particular architectural design space. Each design point in the design space can be characterized by its performance, including latency and throughput, resource consumption and power efficiency. Typically, a framework would employ a mathematical model of the hardware with the aim to predict how a particular design point performs and investigate how to influence its performance. Design Space Exploration (DSE) refers to the task of traversing the design space and selecting one among the alternative design points based on an application-specific objective. This enables a trade-off

between attainable performance and resource distribution and utilization across the multiple tunable parameters of the architecture, under the resource constraints of the target platform for any given CNN model.

Parameter space. The proposed architecture of each framework provides different degrees of freedom for customization, expressed in terms of a set of parameters. fpgaConvNet employs a Synchronous Dataflow (SDF) model [48] to capture both the workload and the hardware mapping of CNNs and express them as SDF graphs. Each layer of the input CNN is mapped to a series of coarse hardware blocks, with each block represented as a node of the graph. The architectural space is traversed by applying a set of transformations over the SDF graph representation of the CNN hardware, such as (1) coarse-grained and (2) fine-grained folding of blocks, (3) graph partitioning with full FPGA reconfiguration, and (4) weights reloading. The folding transformations are used to control the degree of time-multiplexing of each block and influence its performance and resource consumption. The FPGA reconfiguration is used to partition the CNN into several subgraphs and effectively change the hardware as the data flow through the CNN, with one optimized hardware design (and bitstream) per subgraph. In this case, batch processing is used to amortize the reconfiguration overhead, with (5) the batch size being a configurable parameter. The weights reloading transformation includes the generation of a single flexible architecture that can be configured at run time to execute different parts of the CNN, by loading different weights from the memory and changing the datapath.

Similarly, FINN's strategy to maximize performance entails the tailoring of each hardware block along the generated streaming architecture to its layer's workload. To achieve the required performance, the processing rate between the blocks has to be balanced, since the slowest block determines the overall throughput of the system. CONV and FC layers are converted to a matrix multiplication between the trained weights and the layer's inputs. With the MVTU being the core computation engine for these operations (Section 2.3), FINN contains a mechanism to fold and time-multiplex the MVTU. Each MVTU in the architecture is compile-time configurable with respect to two parameters: (1) the number of PEs per MVTU and (2) the number of SIMD lanes per PE, which correspond to the *neuron* and *synapse folds*, respectively, following FINN's terminology.

DeepBurning's accelerator generation is performed by a hardware generator and a compiler in two steps. As a first step, the hardware generator processes the description of a neural network and creates a baseline architecture. This is achieved by selecting appropriate blocks from Deep-Burning's library of neural network components and connecting them as necessary, to create a streaming architecture, as happens in fpgaConvNet and FINN. In the second step, the compiler tunes each block in the architecture so that the accelerator complies with the target FPGA resource constraints. Each block can be configured using (1) temporal folding, where several layers share the same hardware block, and (2) spatial folding, where a single layer is partitioned and all parts are processed by the hardware block in a time-multiplexed manner.

AutoCodeGen instantiates one hardware block per CNN layer. Similarly to FINN, the rate of processing between blocks has to be balanced by tuning the parallelism degree of each hardware block. Each CONV block is compile-time configurable with respect to (1) the number of convolver groups and (2) the number of convolvers per group. Accordingly, each FCcore (Section 2.3) is configurable, with respect to (3) the size of the multiplier array and the corresponding adder tree.

In DNNWEAVER, the input CNN is mapped to a dataflow-based intermediate representation, similar to fpgaConvNet. Each node represents an instruction from DNNWEAVER's custom instruction set, with one instruction associated with each layer. The adopted dataflow representation differs from fpgaConvNet's SDF model in that it is utilized to obtain a high-level model of the CNN's workload while fpgaConvNet employs SDF to model both the CNN workload and its hardware mapping. The architectural template is parameterized and tunable with respect to (1) the number of PUs and (2) the number of PEs per PU as described in Section 2.3, as well as with respect to (3) the scheduling of operations. The scheduling is controlled via the tiling factors for each layer's output feature maps, which is processed by each PU, and influences the amount of communication with the off-chip memory.

Caffeine adopts a uniform representation for both the CONV and FC layers, which allows the reuse of the same hardware for both layers, as happens in FINN. The design parameters to be optimized include (1) the tiling factors along the three dimensions of the input and output feature maps, (2) the tiling factors of the kernels in CONV layers, and (3) the batch size.

SysArrayAccel interprets CONV layers as nested loops. Analytical performance and resource consumption models have been constructed for the systolic array hardware, which are parameterized with respect to (1) the data reuse patterns of the nested loops and (2) the shape of the array. Given a target CNN, different data reuse strategies yield different degrees of parallelism and correspond to selecting two of the nested loops to be mapped on the two dimensions of the systolic array and one loop on the parallel MACC resources of each PE. The shape of the array consists of three parameters that determine the size of each of the two dimensions in the array and the number of parallel MACC units in each PE. SysArrayAccel's tunable parameters enable the exploration along different data reuse strategies and the shaping of the computation engine with three degrees of freedom, to traverse the throughput-resource cost space.

ALAMO generates an accelerator by integrating a set of parameterized modules. Depending on the amount of resources of the target device and the distribution of computational workload in the target CNN, different degrees of parallelism (1) within an input feature map and (2) across output feature maps are exploited. FFTCodeGen instantiates N-point FFT and IFFT hardware blocks for converting feature maps between the space and frequency domains (1) with N being a design parameter. The two blocks are individually parameterized with respect to (2) the folding factor of each pipeline. The HAC unit (Section 2.3) is also parameterized with respect to (3) the number of MACC operators. Finally, (4) the buffer sizes for feature maps and weights are also tunable.

In contrast to the previously described approaches, Angel-Eye's, FP-DNN's, and Snowflake's design principle dictates that the hardware architecture should be independent of the CNN workload. In accordance to this approach, Angel-Eye's generated architecture is parameterized with respect to (1) the number of PEs and (2) the number of convolvers per PE as described in Section 2.3 and their values are selected so that the resource utilization of the target platform is maximized. Similarly, FP-DNN configures its main computation block based only on the available resources of the target platform. As a result, FP-DNN's Matrix Multiplication (*MM*) engine is compile-time configurable with respect to (1) tile size, which is set so that *MM*'s throughput matches the off-chip memory bandwidth of the target platform. Moreover, FP-DNN adopts a resource-sharing strategy for the available on-chip memory resources by organizing the on-chip memory as a pool of buffers, with (2) the allocation schedule of each buffer left as a parameter for the DSE. Finally, Snowflake can be scaled at compile time only with respect to (1) the number of compute clusters based on the available resources of the target device, while the number of compute units (CUs) and MACC operators per CU are fixed.

In a different approach to the rest of the toolflows, HADDOC2 captures the input CNN as a dataflow graph of actors and maps each actor to a physical dedicated hardware block, via a process named Direct Hardware Mapping (DHM). With this approach, the architecture is generated deterministically following the exact topology of the network, without configurable parameters.

Design space formulation and search. The existing FPGA frameworks adopt different levels of analysis for design space exploration, which leads to different DSE methods. fpgaConvNet and DNNWEAVER cast the DSE as a formal constrained optimization problem subject to the resource

budget of the target FPGA. In each case, the objective function is a mathematical performance model of the hardware, with fpgaConvNet offering either throughput maximization [86], latency minimization [88] or multiobjective criteria [85] (such as latency-constrained throughput maximization) based on the user's needs, while DNNWEAVER focuses on throughput maximization and employs batch processing. Due to the large parameter space that would make a brute-force enumeration intractable, both frameworks employ heuristic search methods to obtain a solution to the optimization problem. DNNWEAVER employs a proprietary search algorithm while fpgaConvNet utilizes a custom global optimizer based on the Simulated Annealing algorithm [71].

Following a different approach, Caffeine bases its DSE on an enhanced version of the roofline model [93, 99]. The refined roofline model yields a better estimate of the effective off-chip memory bandwidth by making it dependent on the burst length of each transfer. In contrast to DNNWEAVER and fpgaConvNet, Caffeine's adoption of the higher-level roofline-based modeling leads to a relatively small design space, which enables exhaustive enumeration, with the roofline model used to select the design point with the highest throughput subject to the target platform's memory bandwidth and FPGA resources. To limit the latency overhead caused by batch processing, Caffeine converts FC layers to CONV with a method that allows even small batches to reach high throughput.

SysArrayAccel's DSE formulation lies closer to fpgaConvNet's analytical high-level modeling. Emphasis is placed on constructing accurate performance and resource models of the hardware given the selected data reuse patterns and the shape of the systolic array, and casting the DSE as an optimization problem that aims to maximize throughput. The analytical approach of SysArrayAccel leads to a high-dimensional design space, which makes DSE a difficult task. While fpgaConvNet and DNNWEAVER employed a global optimizer and a heuristic search algorithm, respectively, to address this issue, SysArrayAccel applies a number of pruning strategies, including only the consideration of design points that demonstrate high consumption of the FPGA resources, to reduce the design space and make an exhaustive enumerative search feasible. As a result, although SysArrayAccel substitutes Caffeine's roofline-based modeling with analytical models, both frameworks employ exhaustive enumeration for the selection of the highest-throughput design point subject to the target off-chip memory bandwidth and FPGA resource constraints.

FFTCodeGen formulates DSE in a manner that combines the analytical approaches of fpgaConvNet, DNNWEAVER and SysArrayAccel, with the roofline model of Caffeine. A roofline model is developed as a function of the number of points (N) of the FFT, to obtain the value of N that balances the computation-to-communication ratio for the input CNN on the target platform. FFT-CodeGen's DSE expresses the computational roof as a function of N and captures the computationto-communication bound of the target device by means of a single custom metric, named *device coefficient*. This formulation enables the efficient traversal of the high-dimensional design space and differs to the strategies of fpgaConvNet, DNNWEAVER and SysArrayAccel to handle large design spaces. After the highest performing N for the target CNN-FPGA pair has been determined, the analytical models are used to obtain the rest of the tunable parameters in a closed form. FFT-CodeGen optimizes for high throughput, with customisable constraints on the number of points of the FFT and the batch size to also support latency-driven applications.

FINN's objective is to reach a user-defined throughput. The framework's synthesizer module is responsible for determining the values for the folding parameters, using the balancing of the processing rates of all Matrix-Vector-Threshold Units as a heuristic. Besides throughput maximization, FINN's generated hardware design is also optimized with respect to latency, since no batching of inputs is required. With an approach close to FINN's, DeepBurning's compiler performs a heuristic search to set the folding parameters of the generated hardware to comply with the resource constraints. Similarly to FINN, the generated design runs with a batch size of 1 and hence both

throughput and latency are optimized simultaneously. In resemblance to SysArrayAccel and fpgaConvNet, AutoCodeGen employs high-level analytical performance and resource models to set the tunable parameters of each instantiated hardware block, with balancing the processing rates of all hardware blocks as a heuristic, in a similar approach to FINN.

FP-DNN's mapping strategy focuses on reusing the FPGA resources across layers. With respect to computational resources, the tile size of the single Matrix Multiplication engine is heuristically selected to match the off-chip memory bandwidth of the target platform. With respect to memory resources, the allocation schedule of the pool of on-chip buffers is cast as a graph coloring problem that is solved algorithmically, by taking into account the time slots during which the data of each buffer have to remain intact and aiming to find a feasible reuse schedule that maximizes buffer utilization.

ALAMO's DSE focuses on the instantiation of the appropriate hardware blocks, the scaling of each block and the scheduling of layers. The structure of the compute engine is derived based on the topology and layers of the input CNN. After the necessary modules have been instantiated, the compiler's heuristic considers the resource budget of the target FPGA device and determines the unroll factors within an input feature map and across the output feature maps of each layer, to scale the 2D array of MACC operators and the POOL block (Section 2.3). ALAMO is designed to operate with a batch size of 1 and therefore throughput and latency are co-optimized.

In contrast to the rest of the toolflows, Angel-Eye's and Snowflake's hardware generation are CNN-independent and rely only on the available resources. Each of the two frameworks has a compiler that translates the input CNN to a series of instructions for the accelerator in a heuristic manner. The DSE process includes the CNN-to-instructions mapping, with throughput maximization as an objective. When several mappings with equal performance are possible, Angel-Eye's compiler prioritizes mappings that minimize the off-chip memory accesses to reduce the bandwidth requirements and power consumption. Moreover, Snowflake's compiler performs optimizations based on the structure of the target CNN, including loop removal, unrolling and rearrangement, and includes a communication load balancing technique to sustain a high utilization of the compute resources. Similarly to FINN and DeepBurning, Angel-Eye and Snowflake are designed to operate with batch size of 1 and hence throughput and latency are co-optimized.

Haddoc2's DHM approach performs a one-to-one mapping between the target network and the generated hardware, without considering the specifications of the target platform. As a result, given an input CNN, the toolflow deterministically generates a hardware design independently of the available resources, and the resulting design is feasible only if it fits within the resource budget of the target device. Moreover, the generated architecture operates with a batch size of 1 and hence is optimized for both throughput and latency.

## 2.5 Arithmetic Precision

In FPGA-based CNN implementations, data quantization with few bits has been widely employed. Low-precision fixed-point data representation has been studied to achieve comparable accuracy with high-precision floating-point due to the significant redundancy of the models, while demonstrating a drastic increase in performance [81]. The benefits of employing custom-precision arithmetic are manifold, including reducing the external memory bandwidth requirements (and thus decreasing power consumption due to off-chip memory data transfers), minimizing the on-chip memory footprint, reducing the resource utilization by implementing fixed-point arithmetic units, and thus leading to better hardware efficiency.

Based on the observation that significant variation is demonstrated between the dynamic range of data in different layers of the same network, Angel-Eye employs an automated quantization method to perform dynamic quantization across layers. Given a predefined wordlength for the whole network, different scaling, which determines the radix point position, is selected for each layer. Determining the scaling for each layer is formulated as an optimization problem, solved by a greedy method that minimizes the residual error between the network's outputs when fixed-point and floating-point representations are used. After the scaling of each layer has been selected, the quantized, fixed-point weights are fine-tuned by means of a retraining step, to compensate for the accuracy loss due to quantization.

ALAMO and AutoCodeGen allow the wordlength and scaling of each unit to be adjusted at compile time, so that in layers with narrow dynamic range a longer fractional part will be allocated and vice versa. Similarly, DNNWEAVER features dedicated bits within each instruction (generated by the toolflow's translator module) that dictate whether floating- or fixed-point results should be generated, together with the number of fractional bits and the total bitwidth. Also, in DeepBurning, all components in the hardware library support parameterizable input bitwidth, the value of which is determined by the hardware generator of the toolflow based on the resource constraints.

Caffeine, fpgaConvNet, FP-DNN, SysArrayAccel, and FFTCodeGen provide support for both floating- and fixed-point representations of feature maps and weights. However, a uniform quantization is applied to all layers in all cases, with fixed wordlength and scaling across them. The same approach is followed by HADDOC2, except that only fixed-point representation is supported. Snowflake also employs uniform quantization across all layers but with a fixed bitwidth of 16 bits. Finally, FINN consists almost entirely of binary operations as it focuses on BNNs.

# 2.6 Performance

The most critical characteristic of a CNN-to-FPGA toolflow is the achieved performance of the generated system given a CNN-FPGA pair. An accelerator's primary performance metrics of interest are throughput and latency. A tool's Quality of Results (QoRs) can be evaluated with respect to two factors: (1) comparison with other toolflows for the same CNN-FPGA pair and (2) comparison with hand-tuned accelerators for the same CNN-FPGA pair. Meaningful and fair comparisons across all toolflows would require each toolflow to generate an accelerator for the same CNN targeting the same FPGA device. Nevertheless, the majority of the existing toolflows have not yet been publicly released, which does not allow us to obtain results for the same CNN-FPGA benchmarks. At the moment of writing, DNNWEAVER has an open-source version<sup>16</sup> that provides limited support for the Zynq XC7Z020 platform, HADDOC2 has been open-sourced,<sup>17</sup> FINN has been released in a lightweight version<sup>18</sup> that targets Xilinx's PYNQ-Z1 board and a set of specific BNNs, fpgaConvNet has a dedicated webpage<sup>19</sup> that presents up-to-date benchmarking results on several networks, and Angel-Eye is internally used by DeePhi. Due to this fact, the sole feasible method to evaluate each toolflow's achieved performance is by referring to the reported results either in the corresponding publications or by direct communication with the authors. In this study, we combined both approaches to collect the presented results.

In this section, a performance comparison is presented with the aim to depict an as much as possible well-rounded view of the strengths and weaknesses of each toolflow and draw conclusions about the different mapping strategies. Our evaluation methodology consists of two components: (1) to conduct a fair and meaningful evaluation, we perform direct comparisons only between tools that have mapped the same CNN model on the same FPGA device, and (2) we assess the quality of

<sup>&</sup>lt;sup>16</sup>http://act-lab.org/artifacts/dnnweaver/.

<sup>&</sup>lt;sup>17</sup>https://github.com/KamelAbdelouahab/haddoc2.

<sup>18</sup>https://github.com/Xilinx/BNN-PYNQ.

<sup>&</sup>lt;sup>19</sup>http://cas.ee.ic.ac.uk/people/sv1310/fpgaConvNet.html.

the automatically generated designs by comparing with the current state-of-the-art, hand-tuned designs for the same CNN-FPGA pairs.

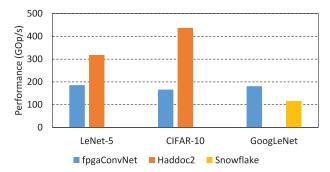

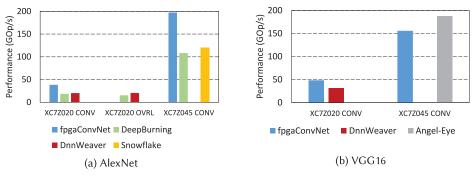

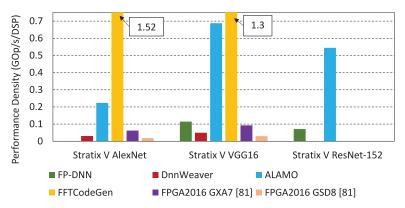

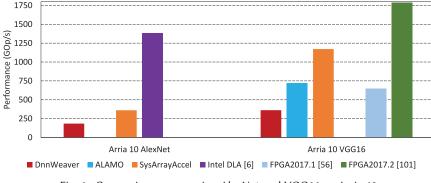

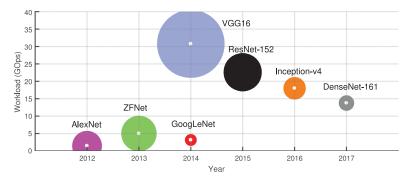

So far, results have been reported on a variety of CNN models, with different tools selecting different benchmarks and devices. Our evaluation is focused on the most commonly mapped AlexNet and VGG16 networks, with a number of additional comparisons on LeNet-5, CIFAR-10, GoogLeNet, and ResNet-152. Detailed results for both the feature extractors (CONV) and the feature extractors followed by classifiers (OVRL)<sup>20</sup> are listed in Tables 2 and 3 for AlexNet and VGG16, respectively, on Zynq and UltraScale platforms and in Tables 4 and 5 for AlexNet and VGG16, respectively, on Stratix V and Arria 10 platforms. Resource-normalizd metrics<sup>21</sup> are also included, since, despite their limitations, which are discussed in Section 3.1, they constitute the current literature standard metric for CNN accelerator comparisons across different devices. For platforms from the same FPGA family and vendor, normalization with respect to LUTs and ALMs can be used. For heterogeneous platforms, normalization with DSPs is employed.

Comparison between toolflows. Figure 4(a) and 4(b) present comparisons of toolflows for the mapping of AlexNet and VGG16 on Zynq platforms. fpgaConvNet, DeepBurning, and DNNWEAVER mapped AlexNet on the resource-limited Zynq XC7Z020 platform (Figure 4(a)). With respect to the feature extractor, fpgaConvNet achieves a throughput of 38.30GOp/s and outperforms DeepBurning and DNNWEAVER by 2.06× and 1.9×, respectively, while for the whole AlexNet, DNNWEAVER reaches 1.34× higher throughput than DeepBurning. With respect to latency, fpgaConvNet's latency-driven methodology yields a 1.37× lower latency than DeepBurning for AlexNet's feature extractor. DNNWEAVER has been optimized for high-throughput applications and requires batch processing to achieve high performance. Therefore, DNNWEAVER's latency has not been considered. When targeting the resource-richer Zynq XC7Z045, fpgaConvNet achieves 1.82× higher throughput and 1.49× lower latency compared to DeepBurning, demonstrating a similar trend to AlexNet on Zynq XC7Z020. Compared to Snowflake, fpgaConvNet reaches 1.64× higher throughput and 1.21× lower latency, with Snowflake achieving 1.11× higher throughput than DeepBurning. With respect to mapping VGG16 on Zynq XC7Z020 (Figure 4(b)), fpgaConvNet achieves 1.22× higher throughput than DNNWEAVER. The gap between the two toolflows is small and possibly due to the finer exploration method of fpgaConvNet.

Both fpgaConvNet and Angel-Eye have mapped VGG16 on Zynq XC7Z045 (Figure 4(b)). Angel-Eye has achieved the current state-of-the-art performance of VGG16 on Zynq XC7Z045 with 1.20× higher throughput than fpgaConvNet for the feature extractor and 136.97 GOp/s for the whole network. Moreover, Angel-Eye achieves 1.52× lower latency than fpgaConvNet.

fpgaConvNet and HADDOC2 have both generated accelerators for the low-end LeNet-5 and CIFAR-10 on Zynq XC7Z045 (Figure 3). In these two cases, HADDOC2 achieves 1.71× on LeNet-5 and 2.63× on CIFAR-10 higher throughput than fpgaConvNet, while using 3-bit and 6-bit bitwidth, respectively, for the two networks compared to the 16-bit representation of fpgaConvNet.

DNNWEAVER and FP-DNN mapped VGG16 and VGG19, respectively, on Stratix V GSD5 (Figure 5). VGG19 has a larger workload compared to VGG16 by having three additional CONV layers. A larger number of CONV compared to FC layers can facilitate an accelerator's performance, since CONV layers are computation bounded. Noting this difference in the VGG19 and VGG16 workloads, we use FP-DNN's performance on VGG19 as an indicator of its throughput on VGG16. In this respect, FP-DNN achieves a throughput of 364.36 GOp/s and outperforms DNNWEAVER by 2.31×.

<sup>&</sup>lt;sup>20</sup>The complete performance results were obtained by contacting the authors.

<sup>&</sup>lt;sup>21</sup>Results are normalized over the available resources of the target device.

| FPGA Platform Zynq XC7Z020<br>Frequency 125 MH <sub>7</sub> | fpgaConvNet     | vNet                    | DeepBurning                     | uming              | DNNWEAVER                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | Snowflake               | Caffeine**              |

|-------------------------------------------------------------|-----------------|-------------------------|---------------------------------|--------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------|-------------------------|

|                                                             |                 | Zynq XC7Z045            | Zynq XC7Z020                    | Zynq XC7Z045       | Zynq XC7Z020                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | Zynq XC7Z045            | UltraScale KU060        |

|                                                             | 1.              | 125 MHz                 | 100 MHz                         | 100 MHz            | 150 MHz                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 250 MHz                 | 200 MHz                 |

| Logic Capacity 53.20 kLUTs                                  |                 | 218.60 kLUTs            | 53.20 kLUTs                     | 218.60 kLUTs       | 53.20 kLUTs                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 218.60 kLUTs            | 331.68 kLUTs            |

| DSPs <sup>*</sup> 220                                       | -6              | 006                     | 220                             | 900                | 220                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 006                     | 2760                    |